### PhD Thesis

# Cache Design Strategies for Efficient Adaptive Line Placement

Dyer Rolán García

2012

Computer Architecture Group Universidade da Coruña, Spain

Computer Architecture Group Universidade da Coruña, Spain

PhD Thesis

# Cache Design Strategies for Efficient Adaptive Line Placement

Dyer Rolán García

April 2012

PhD Advisors: Basilio B. Fraguela Rodríguez Ramón Doallo Biempica

Dr. Basilio B. Fraguela Rodríguez Titular de Universidad Dpto. de Electrónica y Sistemas Universidade da Coruña Dr. Ramón Doallo Biempica Catedrático de Universidad Dpto. de Electrónica y Sistemas Universidade da Coruña

#### CERTIFICAN

Que la memoria titulada "*Cache Design Strategies for Efficient Adaptive Line Placement*" ha sido realizada por D. Dyer Rolán García bajo nuestra dirección en el Departamento de Electrónica y Sistemas de la Universidade da Coruña y concluye la Tesis Doctoral que presenta para optar al grado de Doctor en Ingeniería Informática con la Mención de Doctor Internacional.

En A Coruña, a 27 de Marzo de 2012

Fdo.: Basilio B. Fraguela Rodríguez Director de la Tesis Doctoral Fdo.: Ramón Doallo Biempica Director de la Tesis Doctoral

V° B°: Juan Touriño Domínguez Director del Dpto. de Electrónica y Sistemas

The Dissertation Committee for Dyer Rolán García certifies that this is the approved version of the following dissertation:

#### Cache Design Strategies for Efficient Adaptive Line Placement

Committee:

President,

Member,

Member,

Member,

Secretary,

### Resumen

#### Introducción

Las memorias caché, o simplemente cachés, representan un papel crucial en el rendimiento de las computadoras salvando la diferencia de velocidad que existe entre los procesadores y la memoria principal. La gestión de memorias caché ha adquirido aún más relevancia debido a la aparición de los procesadores multinúcleo (CMPs), que suponen requisitos de ancho de banda superiores, mayores conjuntos de trabajo de aplicaciones emergentes y que además requieren una distribución eficiente de los recursos caché entre todos los núcleos de procesamiento.

Esta Tesis se centra en analizar algunos de los problemas que se encuentran habitualmente en las cachés modernas y propone soluciones efectivas y económicas para mejorar su rendimiento. La mayoría de los diseños propuestos en esta Tesis son capaces de reducir la tasa de fallos basándose en los diferentes niveles de demanda de cada conjunto caché. De este modo, las líneas caché se ubican en bloques infrautilizados de otros conjuntos caché si es probable que vuelvan a ser referenciadas y su conjunto nativo está experimentando problemas de capacidad. Cuando esto no es suficiente, esta Tesis propone modificar de un modo coordinado la política de inserción de estos conjuntos caché. Por tanto, nuestras propuestas retienen la mayor parte útil del conjunto de trabajo a la vez que descartan datos temporales tan pronto como sea posible. Estas ideas, inicialmente aplicadas en cachés de último nivel, en inglés Last-Level Caches (LLCs), de monoprocesadores, son adaptadas satisfactoriamente en esta Tesis a cachés de primer nivel y sistemas multinúcleo. En cuanto a las cachés de primer nivel, proponemos un diseño novedoso que permite la distribución de recursos caché entre instrucciones y datos dependiendo de sus necesidades particulares. A continuación, en sistemas multinúcleo, nuestros diseños son en un primer momento mejorados mediante la inclusión de soporte para tratar cada hilo que comparte recursos en una caché compartida de un modo particular para, a continuación, proponer una política de inserción específicamente diseñada para este entorno. Finalmente, exploramos la compartición de recursos en CMPs con LLCs privadas mediante el desplazamiento de líneas entre las distintas cachés que constituyen el último nivel de la jerarquía. Este último diseño incluye además varios puntos novedosos como la inclusión de un estado neutral en el mecanismo de desplazamiento que impide que un conjunto caché tome parte en el mismo si esto pudiese llegar a ser perjudicial, el uso de distintas granularidades para la gestión de la caché o la aplicación coordinada de la política de inserción más conveniente con los mecanismos previos. A lo largo de todo este proceso hemos usado una métrica sencilla y efectiva para determinar el estado, o nivel de saturación, de los conjuntos caché llamada Set Saturation Level (SSL). Finalmente, cabe destacar que nuestros diseños se han mostrado muy competitivos con respecto a otras propuestas recientes, incluso a menudo superándolas, a pesar de suponer costes de almacenamiento y consumo de energía casi insignificantes.

#### Metodología

El desarrollo de esta Tesis sigue las líneas de metodologías clásicas; incluyendo planificación, diseño, análisis de costes, evaluación y viabilidad de las implementaciones propuestas. El principal objetivo de esta Tesis es enriquecer el diseño moderno de memorias caché mediante la propuesta de nuevas políticas para monoprocesadores y su posterior adaptación a procesadores multinúcleo. Veremos que si bien los diseños para los primeros son directamente aplicables a los segundos, estos diseños deben adaptarse si queremos alcanzar el mejor nivel de prestaciones en los procesadores multinúcleo.

En primer lugar, se desarrolló un estudio cuidadoso del estado del arte en el campo de las memorias caché, inicialmente en el último nivel de la jerarquía. Como resultado, se detectaron y analizaron comportamientos perjudiciales y debilidades en diseños previos y se propusieron soluciones eficientes. En segundo lugar, se realizó la configuración de un entorno adecuado para la evaluación de las soluciones propuestas. A continuación, se depuraron y ajustaron los diseños propuestos para obtener un rendimiento óptimo con un coste adicional poco significativo. Estos diseños previos, que se evaluaron exitosamente en entornos monoprocesador, fueron sucesivamente adaptados a entornos con procesadores multinúcleo siguiendo las mismas fases.

Finalmente, todos estos esfuerzos han contribuido a lograr el objetivo principal de mejorar el rendimiento de las memorias caché manteniendo el mismo grado de complejidad que en el funcionamiento caché tradicional, bajo consumo de potencia y costes de almacenamiento adicionales mínimos. De hecho estos diseños han superado a las técnicas más recientes en este campo, tanto para entornos monoprocesador como para procesadores multinúcleo.

#### Conclusiones

A fin de neutralizar la diferencia de velocidad entre el procesador y la memoria principal, los procesadores modernos cuentan con grandes cachés de último nivel (LLC). Sin embargo, los diseños tradicionales, originalmente desarrollados para pequeñas cachés de primer nivel, son ineficientes para cachés mayores y LLCs compartidas en procesadores multinúcleo. La importancia de la gestión de la caché se ha vuelto más crítica debido al aumento de los requisitos de ancho de banda de los CMPs, el incremento de los conjuntos de trabajo de aplicaciones emergentes, y el menor espacio de caché dedicado a cada procesador debido al aumento del número de procesadores por chip. Esta Tesis, "Cache Design Strategies for Efficient Adaptive Line Placement", analiza algunos de los problemas que aparecen al gestionar grandes cachés y los comportamientos perjudiciales que experimentan para así proponer soluciones efectivas y aumentar su rendimiento. De hecho, esta Tesis demuestra que cambios sencillos y con un coste adicional mínimo pueden incrementar substancialmente el rendimiento de estas cachés. Una característica común a todos los diseños propuestos en esta Tesis es que analizan y aplican políticas de grano fino para mejorar el rendimiento sin que ello implique un coste de almacenamiento elevado ni grandes modificaciones en el funcionamiento habitual de la caché.

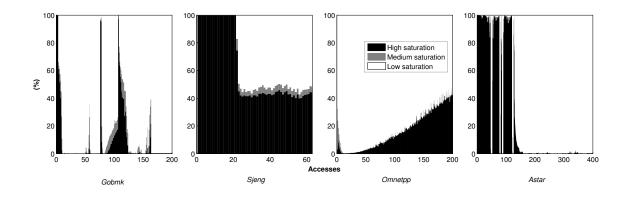

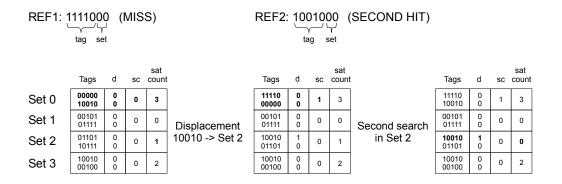

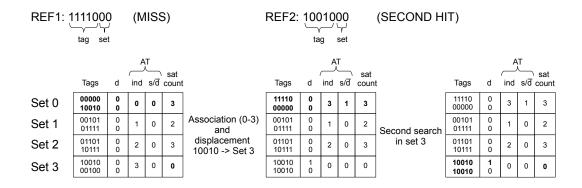

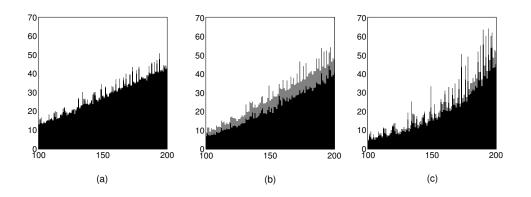

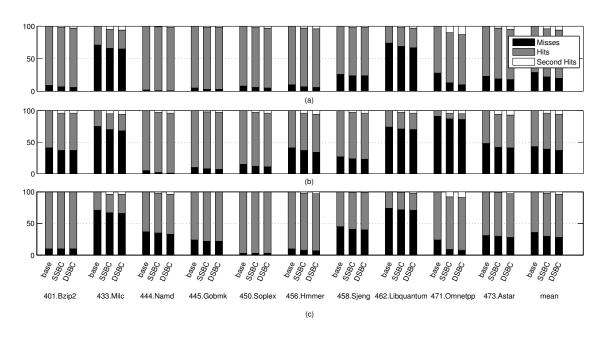

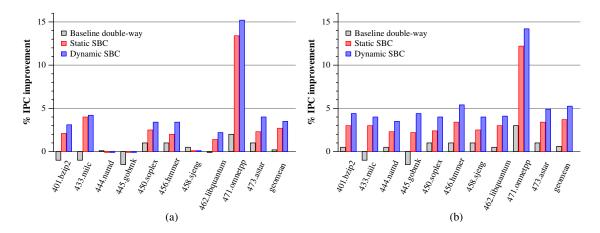

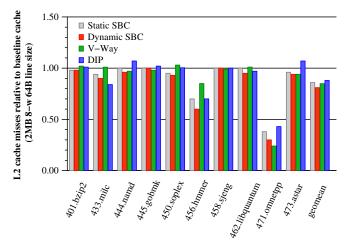

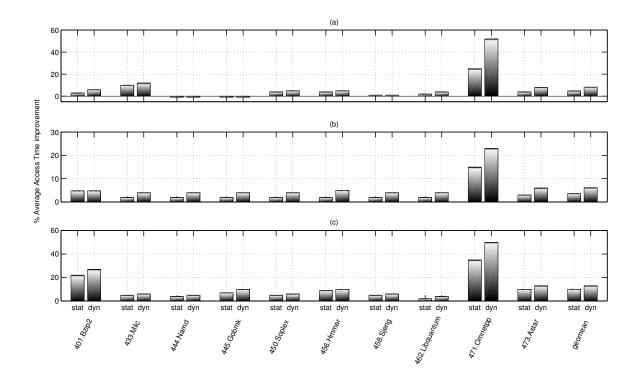

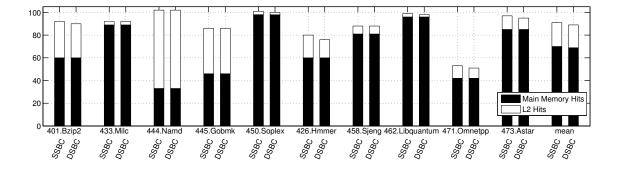

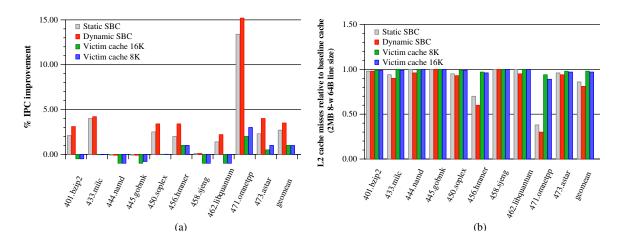

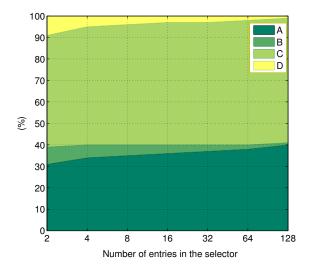

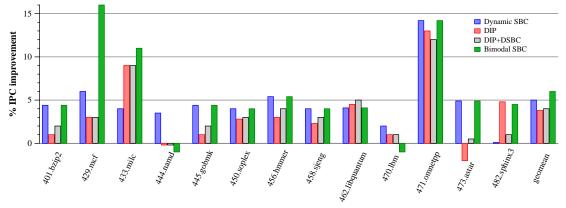

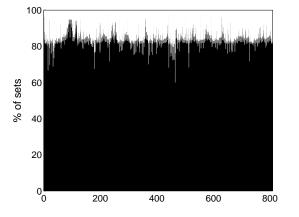

Esta Tesis demuestra que los efectos perjudiciales derivados de una de las ineficiencias más comunes en las memorias caché, la no uniformidad de las referencias a memoria sobre los distintos conjuntos caché, puede reducirse mediante el desplazamiento de líneas desde conjuntos que requieren más espacio hacia otros que pueden proporcionarlo mediante el establecimiento de asociaciones entre ellos. La Set Balancing Cache (SBC) [60] asocia estas dos clases de conjuntos con el fin de equilibrar la carga de datos entre ellos. Para determinar el estado de cada conjunto la SBC utiliza una métrica sencilla y efectiva denominada Set Saturation Level (SSL), que mide hasta qué punto es capaz un conjunto dado de la caché de retener su conjunto de trabajo particular. Este valor se calcula para cada conjunto gracias a un contador con aritmética de saturación que se incrementa con cada fallo caché que se produce en el conjunto y se reduce con cada acierto. Esta métrica ha demostrado ser capaz de establecer el rol más adecuado de cada conjunto dentro de una asociación. Un diseño estático inicial (SSBC), el cual permite únicamente desplazamientos entre parejas de conjuntos preestablecidas, logró una reducción media en la tasa de fallos de 9.2%, o 14% si se calcula en términos de media geométrica. Esta reducción resultó en una mejora media en el IPC entre 2.7% y 3.7% dependiendo de la configuración usada. Además, se propone una estructura sencilla y económica, llamada Destination Set Selector (DSS), capaz de proporcionar el conjunto libre dentro de la caché más conveniente para recibir líneas ante una solicitud de asociación. Una versión dinámica mejorada de la SBC (DSBC), la cual asocia conjuntos caché altamente saturados con aquellos menos saturados gracias al DSS, obtuvo una reducción media en la tasa de fallos de 12.8%, 19% computado como la media geométrica, consiguiendo una mejora en el IPC de entre 3.5% y 5.25% dependiendo de la jerarquía de memoria considerada. Finalmente, los distintos diseños de la SBC demostraron consistentemente ser mejores que sucesivos incrementos en la asociatividad, tanto en términos de área requerida como rendimiento, además de suponer costes de almacenamiento mínimos; menos de un 0.6% con respecto a la configuración base.

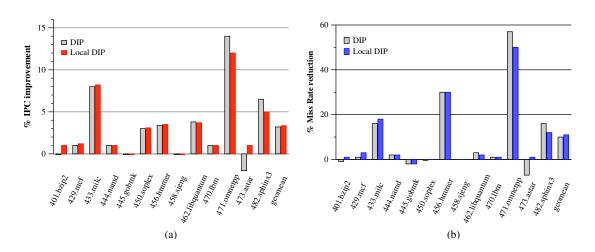

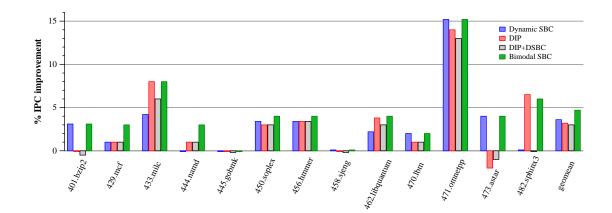

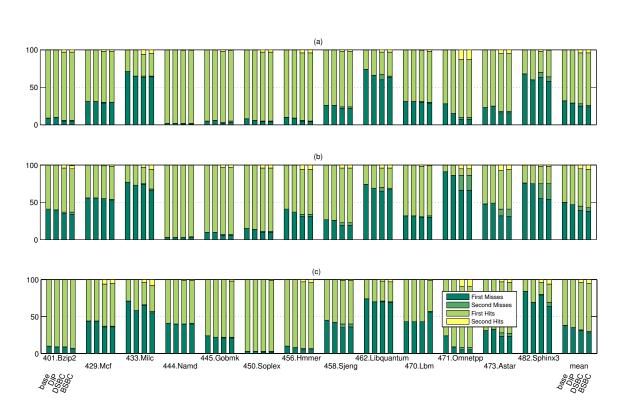

Esta Tesis confirma además que otro de los problemas más habituales en las memorias caché, el *thrashing*, puede aliviarse mediante la aplicación de una política de inserción capaz de descartar datos temporales lo antes posible a la vez que mantiene la sección con más localidad del conjunto de trabajo en la caché. Este tipo de política puede combinarse con la DSBC propuesta en esta Tesis para reducir la presión sobre los conjuntos caché cuando el desplazamiento de líneas entre los mismos no es suficiente. Inicialmente se analizan las razones que llevan a un comportamiento no óptimo de la combinación entre la DSBC y una política de inserción

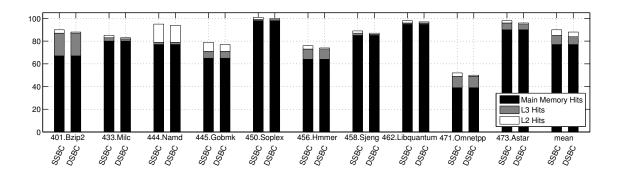

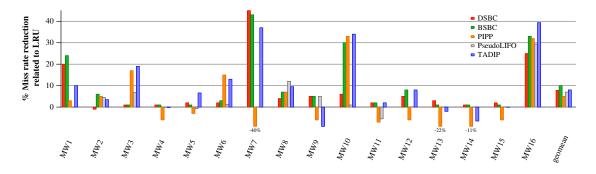

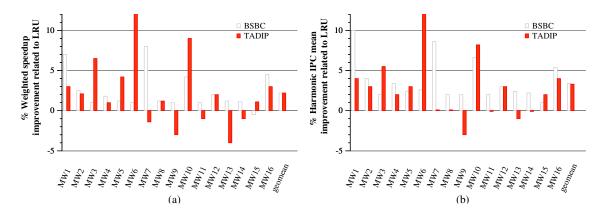

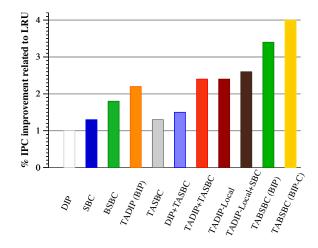

específicamente diseñada para atacar problemas de capacidad como es la Dynamic Insertion Policy (DIP) [53] en una caché. En base a ello, se propone de un modo razonado un diseño integrado de ambas políticas que permite su cooperación efectiva: la Bimodal Set Balancing Cache (BSBC) [61]. Este diseño extendido trata con fallos de conflicto y de capacidad mediante el uso del Set Saturation Level como único árbitro de control de ambos comportamientos. Por tanto, esta Tesis demuestra además la utilidad del SSL para detectar problemas de capacidad globales en la caché así como desequilibrios entre conjuntos. De este modo, la BSBC implica sólo un 0.6% de coste de almacenamiento adicional con respecto a la caché base. Experimentos usando benchmarks con características variadas muestran que la aplicación conjunta de la DSBC y DIP en una caché puede resultar un diseño poco afortunado si no se coordina adecuadamente, o que, por el contrario, puede proporcionar los mejores resultados cuando se integran apropiadamente en nuestro diseño BSBC. Por ejemplo, en una caché de segundo nivel de 2MB y 8 vías, la combinación sin coordinación de ambas propuestas, DIP+DSBC, obtiene una reducción relativa en la tasa de fallos de 8.3 %, mientras que la DSBC y DIP de un modo aislado la reducen en un 12% y un 10% respectivamente. Con la BSBC la reducción asciende hasta el 16 %. Como resultado, la BSBC consigue las mayores mejoras en términos de IPC, 4.8% para la misma configuración, en comparación con el 3% que proporciona la combinación sin coordinación DSBC+DIP. El resto de políticas probadas; DSBC, DIP y la probabilistic escape LIFO, obtienen resultados intermedios. Por tanto, esta Tesis muestra que la coordinación de distintas políticas para tratar distintos problemas puede gestionarse con sencillas y económicas métricas y proporcionar beneficios mucho mayores que la aplicación independiente de dichas políticas. Adicionalmente, hemos demostrado que la BSBC es directamente aplicable a una caché compartida, donde se ha desenvuelto favorablemente, logrando una reducción media del 10%en la tasa de fallos y una mejora en el IPC del 3%, superando incluso a técnicas específicamente diseñadas para rendir en este tipo de entorno como PIPP [84]. También se ha evaluado la DSBC en una caché compartida, reduciendo la tasa de fallos en un 7.8% y logrando una mejora en la productividad de hasta un 10%. A pesar de estos resultados positivos, técnicas que incluyen soporte para tratar a cada hilo de un modo independiente, como TADIP [27], han obtenido mejores resultados a medida que se incrementa el número de procesadores que comparten los recursos. Esto sugiere la importancia de dar un tratamiento particular a cada flujo de acceso

independiente en la caché.

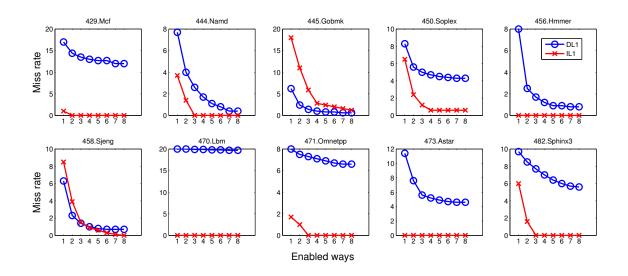

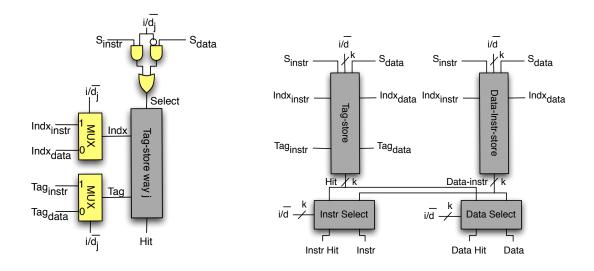

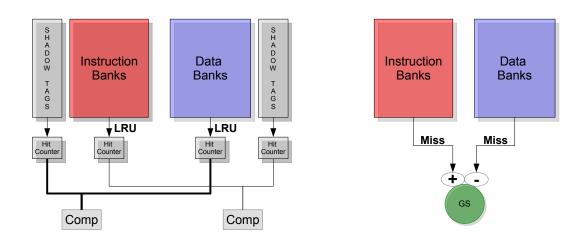

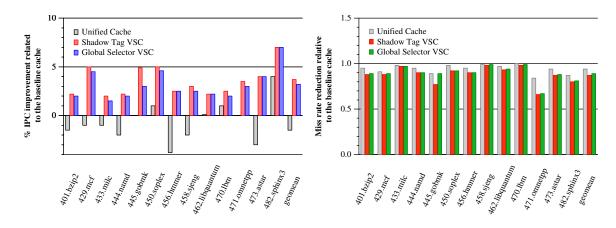

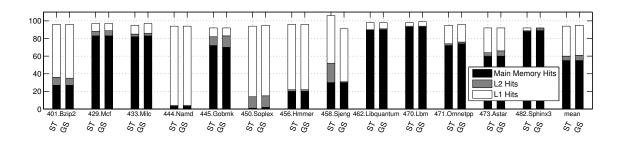

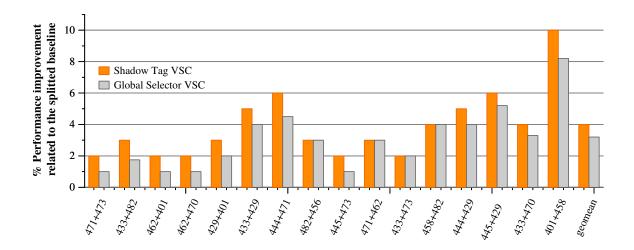

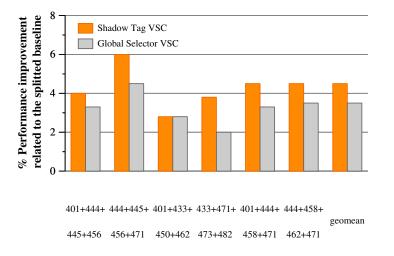

A continuación esta Tesis muestra que la idea de dar tratamientos particulares a distintos flujos de acceso de acuerdo a su comportamiento individual puede aplicarse satisfactoriamente a cachés de primer nivel mediante el ajuste dinámico de los recursos destinados a instrucciones y datos, los dos principales flujos de acceso que existen a este nivel de la jerarquía, dependiendo de su demanda particular. Proponemos la Virtually Split Cache (VSC), el primer diseño que es consciente de la distinta localidad que tienen las instrucciones con respecto a los datos y que reserva recursos, específicamente bancos de memoria, para ambos tipos de información dependiendo de la demanda de cada uno. Hemos propuesto dos diseños alternativos para determinar los recursos que demandan tanto instrucciones como datos. El primer diseño, la Shadow Tag VSC, usa etiquetas extra para decidir si asignar un banco de memoria adicional para instrucciones, o datos, aumenta el rendimiento. El segundo diseño, la Global Selector VSC, usa un contador común con aritmética de saturación para que instrucciones y datos se batan en duelo por los recursos. La Shadow Tag VSC logró un 3.7% de mejora en el IPC, una reducción media en la tasa de fallos del 13% y una reducción en el consumo de potencia de la jerarquía de memoria del 10%, con respecto a un diseño caché separado para instrucciones y datos. La Global Selector VSC obtuvo un 3.2% de mejora en el IPC y una reducción media en la tasa de fallos del 11%, necesitando sólo 4 bits de almacenamiento adicional, mientras que redujo el consumo de potencia en un 8%. Además, ambos diseños demostraron un buen desempeño en entornos multinúcleo. Así, la Shadow Tag VSC y la Global Selector VSC mejoraron una configuración base con 4 procesadores en términos de productividad en un 4.5% y un 3.7% de media, respectivamente.

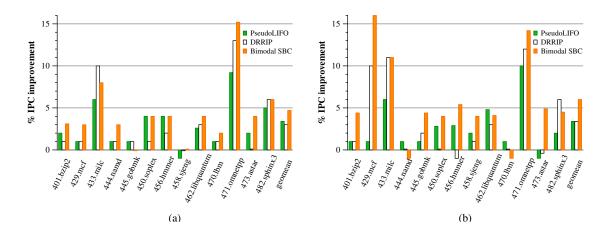

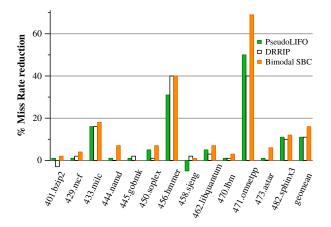

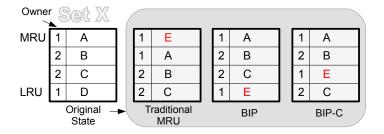

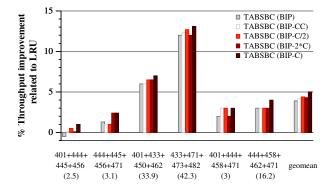

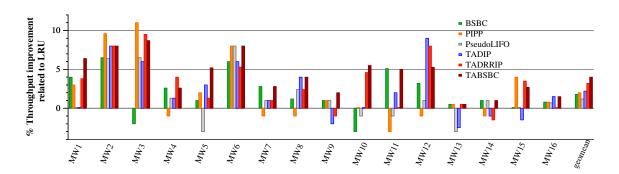

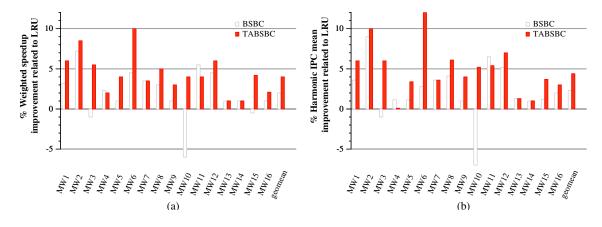

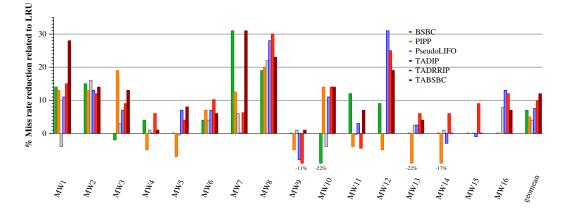

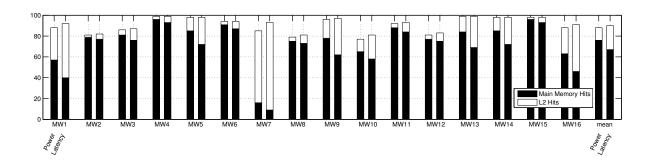

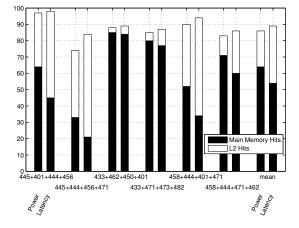

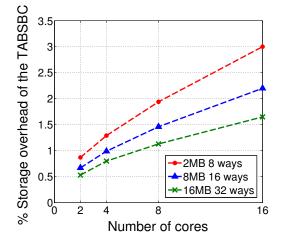

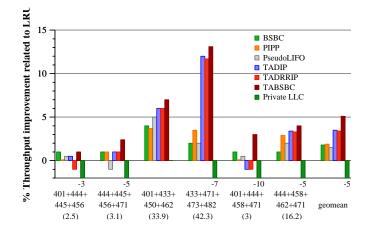

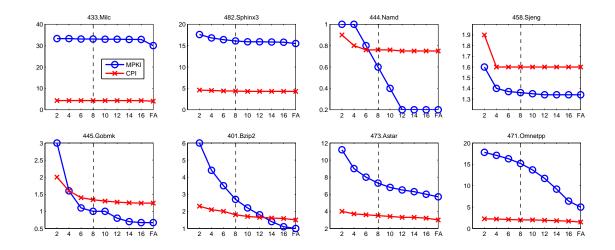

Más adelante esta Tesis se centra en LLCs compartidas, donde pueden encontrarse también los comportamientos analizados previamente. La Thread-Aware Bimodal Set Balancing Cache (TABSBC) mide el nivel de presión que cada aplicación ejerce en cada conjunto de la caché utilizando el Set Saturation Level. Este diseño incluye una nueva política de inserción, llamada BIP-C, específicamente diseñada para reducir problemas de capacidad en cachés compartidas. Esta política supone una mejora considerable con respecto a BIP [53] en estas cachés, puesto que protege a las líneas de ser desalojadas debido a accesos de otros procesadores. Cuando la TABSBC estima que una aplicación está experimentando un mal comportamiento caché, trata en un primer momento de desplazar las líneas de la aplicación problemática hacia conjuntos caché con espacio libre aplicando técnicas basadas en la Set Balancing Cache. Cuando esto no es posible o suficiente, recurre a BIP-C para la aplicación y el conjunto caché en cuestión. La TABSBC proporciona de un modo sensato y coordinado un mecanismo capaz de aplicar sus políticas subyacentes considerando los distintos hilos que comparten los recursos. A pesar de su naturaleza de grano fino su coste de almacenamiento es muy razonable, sobre un 1% o incluso menos en configuraciones representativas. Una extensa experimentación usando una amplia gama de benchmarks indica que la TABSBC consigue consistentemente los mejores resultados en comparación con propuestas recientes. Esto se debe a dos características principales que la distinguen de otras propuestas. La primera es la capacidad de aplicar políticas de grano fino en contraposición a las políticas globales que usan otras técnicas. La segunda es la coordinación de mecanismos capaces de reducir fallos de conflicto y de capacidad. Este último detalle es ignorado por otras propuestas específicamente diseñadas para cachés compartidas. Por estas mismas razones, la TABSBC sigue manteniendo sus buenos resultados a medida que se aumenta el número de procesadores que comparten la caché.

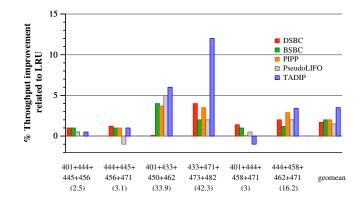

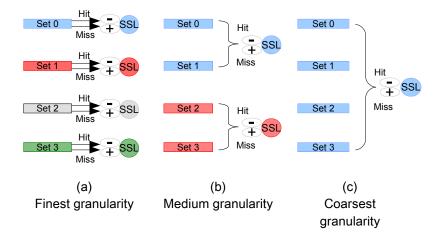

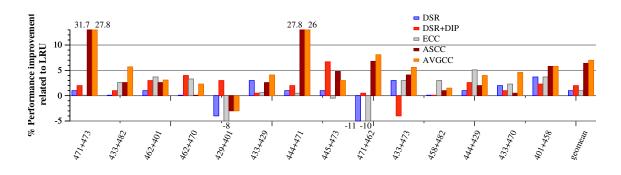

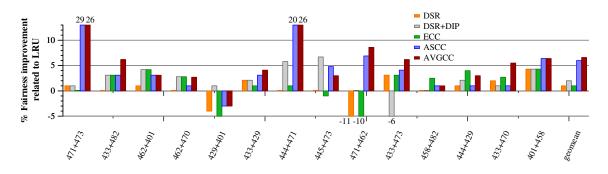

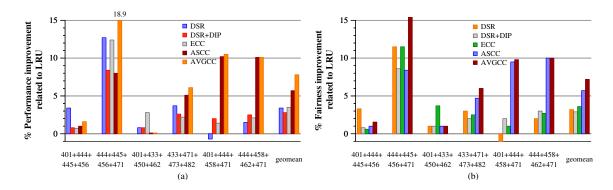

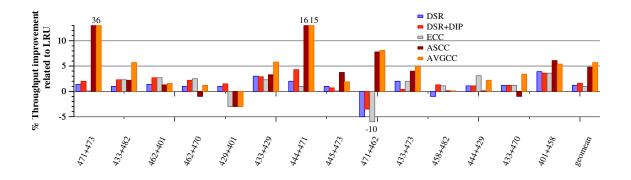

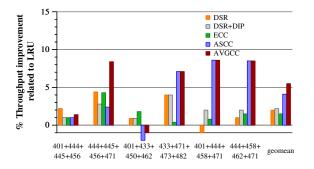

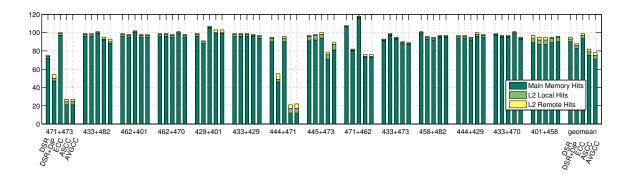

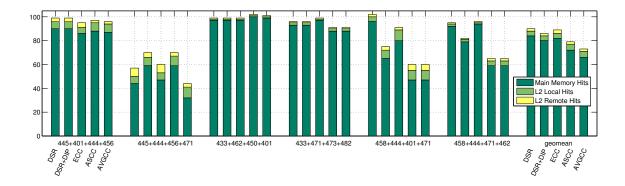

Finalmente, esta Tesis reafirma el hecho de que un modo habitual de incrementar el rendimiento en CMPs con LLCs privadas es proporcionar un mecanismo que habilite la compartición de recursos mediante el desplazamiento de líneas. Proponemos el Adaptive Set-Granular Cooperative Caching (ASCC) [62], un diseño capaz de determinar el estado de cada conjunto caché y aplicar las políticas más adecuadas a cada uno, en comparación con otros diseños que aplican políticas globalmente. Este diseño realiza desplazamientos entre conjuntos de distintas cachés y aplica la política de inserción más conveniente a cada conjunto si los desplazamientos no son suficientes para reducir los fallos de capacidad, apoyándose en el SSL. Proponemos una nueva política de inserción, SABIP, específicamente diseñada para abordar problemas de capacidad en entornos donde se realizan desplazamientos entre cachés. Además, introducimos un estado neutral para conjuntos individuales dentro del mecanismo de desplazamientos, de forma que éstos no participan ni como emisores ni como receptores de líneas en los mismos. Los beneficios de mantener partes de la caché en este estado, es decir, sin tomar parte en el mecanismo de desplazamientos, han demostrado ser cuantiosos. ASCC logró una mejora en el rendimiento del 6.4% y del 5.7\% ejecutando 2 y 4 aplicaciones, respectivamente, lo que se tradujo en una reducción de la latencia media de memoria del 18% y 21%. Su coste de almacenamiento ha sido estimado en un 0.17% con respecto a la configuración base. Además, esta Tesis propone la idea de ajustar dinámicamente la granularidad a la cual se determina el estado de la caché y se aplican las distintas políticas dependiendo de su comportamiento. El Adaptive Variable-Granularity Cooperative Caching (AVGCC) es el primer diseño capaz de adaptar la granularidad dependiendo del comportamiento de la caché para aplicar las políticas del ASCC. En un sistema con 4 procesadores, ejecutando cargas multiprogramadas, AVGCC consiguió una mejora en el rendimiento del 7.8 % con respecto al sistema base. Además, superó con creces el rendimiento de otros diseños suponiendo un coste de almacenamiento adicional mínimo; menos de un 0.2 %. También es importante destacar la reducción en la latencia media a memoria, 27%, y en el consumo de potencia obtenido; menor en un 29%al de una configuración tradicional. Cabe destacar también que se obtuvieron resultados similares utilizando cargas multihilo. Finalmente, esta Tesis demuestra que mejorar un diseño dotándolo de soporte para calidad de servicio, en inglés Quality of Service, no siempre implica una pérdida en el rendimiento medio. Un diseño extendido del AVGCC, denominado QoS-Aware AVGCC, obtuvo una mejora en el rendimiento de un 8.1% a pesar de suponer un coste de almacenamiento adicional casi insignificante; 0.35%.

#### Contribuciones

Las principales contribuciones de esta Tesis son:

- 1. Una nueva métrica sencilla y con un coste reducido, llamada *Set Saturation Level* o SSL, capaz de medir el grado en el que un conjunto de la caché es capaz de alojar su conjunto de trabajo particular y así detectar tanto desequilibrios entre conjuntos como problemas globales de capacidad.

- 2. Un novedoso diseño caché, llamado *Set Balancing Cache* o SBC, capaz de reducir fallos de conflicto mediante la creación de asociaciones entre conjuntos y de controlar el desplazamiento de líneas entre los mismos. Este diseño ha sido evaluado con éxito, superando a las técnicas más recientes en su campo.

Simulaciones exhaustivas han probado la capacidad de este diseño en distintos entornos además de su versatilidad.

- 3. Una combinación coordinada de diseños capaz de reducir fallos de conflicto y de capacidad al mismo tiempo. La *Bimodal Set Balancing Cache* o BSBC, la cual extiende las capacidades de la SBC para reducir fallos de conflicto incluyendo una política de inserción específicamente diseñada para reducir fallos de capacidad, ha sido implementada y evaluada exitosamente.

- 4. Una nueva técnica para equilibrar la cantidad de espacio destinada a instrucciones y datos en cachés de primer nivel: la *Virtually Split Cache* o VSC. Esta técnica combina la capacidad de compartición de recursos de aproximaciones unificadas con el alto ancho de banda y el paralelismo que proporciona una configuración separada.

- 5. Un nuevo entorno, la *Thread-Aware Bimodal Set Balancing Cache* o TABSBC, dotado de soporte para tener en cuenta el comportamiento de los distintos hilos que comparten recursos y que coordina de un modo razonado estrategias orientadas a reducir fallos de conflicto y de capacidad para cachés compartidas en procesadores multinúcleo.

- 6. Finalmente, esta Tesis introduce un nuevo esquema de cachés cooperativas para jerarquías de memoria privadas en CMP: el Adaptive Set-Granular Cooperative Caching o ASCC. Esta técnica combina un mecanismo de desplazamiento de líneas con la aplicación de una política de inserción específicamente diseñada para tratar con problemas de capacidad utilizando el SSL para controlar ambos comportamientos. Se propone también un nuevo estado para los conjuntos en el mecanismo de desplazamiento de líneas, el estado neutral, que impide que un conjunto pueda participar en los desplazamientos si esto puede resultar perjudicial. Además, se extiende esta técnica para dotarla de un mecanismo capaz de establecer la granularidad más adecuada a la cual se aplican las distintas políticas caché: el Adaptive Variable-Granularity Cooperative Caching o AVGCC.

### Publicaciones derivadas de la Tesis

#### Revistas

- D. Rolán, B. B. Fraguela, and R. Doallo. Set Saturation Level-Based Cache Management. In *IEEE Transactions on Architecture and Code Optimization*, 2012 (En revisión).

- D. Rolán, B. B. Fraguela, and R. Doallo. Virtually Split Cache: An Efficient Mechanism to Distribute Instructions and Data in First-Level Caches. In *IEEE Transactions on Architecture and Code Optimization*, 2012 (En revisión).

#### Conferencias internacionales

- D. Rolán, B. B. Fraguela, and R. Doallo. Adaptive line placement with the Set Balancing Cache. In *Proceedings of the 42nd IEEE/ACM International* Symposium on Microarchitecture (MICRO 2009), pages 529–540, Diciembre 2009.

- D. Rolán, B. B. Fraguela, and R. Doallo. Reducing capacity and conflict misses using set saturation levels. In *Proceedings of the 17th International Conference on High Performance Computing* (HiPC 2010), Diciembre 2010.

- D. Rolán, B. B. Fraguela, and R. Doallo. Adaptive Set-Granular Coopera-

tive Caching. In Proceedings of the 18th International Symposium on High Performance Computer Architecture (HPCA 2012), pages 213–224, Febrero 2012.

#### Conferencias nacionales

D. Rolán, B. B. Fraguela, and R. Doallo. Caché con Reequilibrio de Conjuntos. In Actas de las XX Jornadas de Paralelismo, pages 253–258, Septiembre 2009. A Adolfo Rolán Barja, meu avó, para o que sempre serei máis ca un "enxeñeiro".

### Acknowledgments

It is embarrassing to admit that this Thesis<sup>1</sup> starts as lax as its cover page states. Although it lists my name as the single author, it is fair to say that the content and ideas in the following pages arose from the effort of many people, and to them, without exception, I owe my thanks.

My advisors gave me the opportunity and the confidence I needed to undertake this task and did their best to teach me how to get involved in research these past several years. Thanks to Ramón, also for guiding this work with all his experience, and Basilio, whose ability to see problems right through solutions is simply commendable.

Next and foremost, there is no word or sentence good enough to give thanks to my loving parents, who long before the University taught me how to fulfill any single wish by means of willpower, persistence and a bit of talent; and to the rest of my family, especially to my siblings. Their unflagging advocacy and optimism have sustained me all along these years.

Many thanks to all the people who belong to the close circle that surrounds the GAC group (specially the *Lab 0.2* guys and Guille, who has provided me with the  $L^{T}EX$  template for this Thesis, among other things). They have graciously shared their time and thoughts with me either in dinner parties, coffee breaks and trips.

I am also unspeakably thankful to those people who have warmly welcome me wherever I have been through these years, especially Jose Renau and the guys from the MASC group and their close friends (Ehsan, Elnaz, Amir, Rigo...) in California, and Marcelo and the CArD group staff back in Edinburgh.

I do not want to forget those people who enabled me to stop thinking about this work, even just for a while. Thanks to my school of languages classmates (especially

<sup>&</sup>lt;sup>1</sup>This work was supported by the Xunta de Galicia under projects INCITE08PXIB105161PR and "Consolidación e Estructuración de Unidades de Investigación Competitivas" 3/2006 and 2010/06 and the MICINN, cofunded by the Fondo Social Europeo, under grants with references TIN2007-67536-C03-0 and TIN2010-16735. The author is also member of the HiPEAC network.

Héctor and Ali) and teachers, friends all, and to my outdoor and indoor soccer mates. Their support and friendship have been invaluable.

Last but not least, thanks to you, Raquel, for many times of steadfast friendship and affection. Let me humbly dedicate these ending lines to you in an attempt to begin another wonderful journey ;)

Dyer.

"Research is to see what everybody else has seen, and to think what nobody else has thought" Albert Szent-Gyorgyi

### Abstract

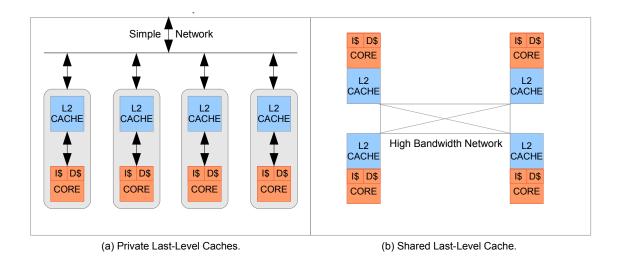

Efficient memory hierarchy design is critical due to the large difference between the speed of the processors and the memory. In this context, cache memories play a crucial role bridging this gap. Cache management has become even more significant due to the appearance of chip multiprocessors (CMPs), which imply larger memory bandwidth requirements and greater working sets of many emerging applications, and which also need a fair and efficient distribution of cache resources between the cores in a single chip.

This dissertation aims to analyze some of the problems commonly found in modern caches and to propose cost-effective solutions to improve their performance. Most of the approaches proposed in this Thesis reduce cache miss rates by taking advantage of the different levels of demand cache sets may experience. This way, lines are placed in underutilized cache blocks of other cache sets if they are likely to be reused in the near future and there is no enough space in their native cache set. When this does not suffice, this dissertation proposes to modify in a coordinated way the insertion policies of oversubscribed sets. Hence, our proposals retain the most useful part of the working set in the cache while discarding temporary data as soon as possible. These ideas, initially developed in the context of last-level caches (LLCs) in single core systems, are successfully adapted in this Thesis to first-level caches and multicore systems. Regarding first-level caches, a novel design that allows to dynamically allocate banks to the instruction or the data cache depending on their degree of pressure is presented. As for multicore systems, our designs are firstly provided with thread-awareness in shared caches in order to give a particular treatment to each stream of requests depending on its owner. Finally, we explore the sharing of resources by means of the spilling of lines among private LLCs in CMPs using several innovative features such as a neutral state, which prevents caches from taking part in the spilling mechanism if this could be harmful, variable granularities for the management of the caches, or the coordinated management of the cache insertion policy. Throughout this process we have used a simple and cost-effective metric to track the state of each cache set called Set Saturation Level (SSL). Finally, it is worthy to point out that our approaches are very competitive and often outperform many of the most recent techniques in the field, despite they imply really small storage and power consumption overheads.

## Contents

| 1. | Intr           | oduction 1                                                    |    |  |  |  |

|----|----------------|---------------------------------------------------------------|----|--|--|--|

|    | 1.1.           | Cache Memories: Basics                                        | 2  |  |  |  |

|    | 1.2.           | Related Work                                                  | 4  |  |  |  |

|    |                | 1.2.1. Related Work in Single Core Environments               | 5  |  |  |  |

|    |                | 1.2.1.1. Reducing Conflict Misses                             | 5  |  |  |  |

|    |                | 1.2.1.2. Reducing Capacity Misses                             | 7  |  |  |  |

|    |                | 1.2.2. Related Work in Multicore Platforms                    | 8  |  |  |  |

|    |                | 1.2.2.1. Cache Memory Hierarchies with Shared Levels          | 8  |  |  |  |

|    |                | 1.2.2.2. Cache Memory Hierarchies with Private Levels $\ .$ . | 9  |  |  |  |

|    | 1.3.           | The Problem                                                   | 10 |  |  |  |

|    | 1.4.           | Thesis Statement                                              | 14 |  |  |  |

|    | 1.5.           | Contributions                                                 | 14 |  |  |  |

|    | 1.6.           | Overview of the Contents                                      | 15 |  |  |  |

| 2. | $\mathbf{Set}$ | Balancing Cache                                               | 17 |  |  |  |

|    | 2.1.           | Introduction                                                  | 17 |  |  |  |

|    | 2.2.           | Background and Motivation                                     | 18 |  |  |  |

|    | 2.3. | Static Set Balancing Cache                          | 20 |

|----|------|-----------------------------------------------------|----|

|    |      | 2.3.1. Association algorithm                        | 21 |

|    |      | 2.3.2. Displacement algorithm                       | 22 |

|    |      | 2.3.3. Search algorithm                             | 23 |

|    |      | 2.3.4. Discussion                                   | 24 |

|    | 2.4. | Dynamic Set Balancing Cache                         | 25 |

|    |      | 2.4.1. Association algorithm                        | 26 |

|    |      | 2.4.2. Displacement algorithm                       | 28 |

|    |      | 2.4.3. Search algorithm                             | 28 |

|    |      | 2.4.4. Disassociation algorithm                     | 29 |

|    |      | 2.4.5. Discussion                                   | 29 |

|    | 2.5. | Simulation environment                              | 30 |

|    | 2.6. | Experimental evaluation                             | 33 |

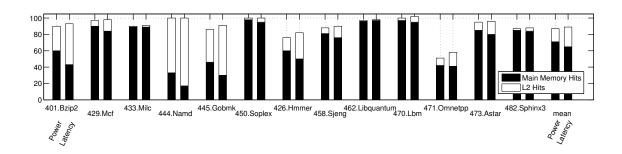

|    |      | 2.6.1. Average memory latency and power consumption | 36 |

|    | 2.7. | Cost                                                | 37 |

|    | 2.8. | Analysis                                            | 41 |

|    |      | 2.8.1. Impact of varying cache parameters           | 41 |

|    |      | 2.8.2. Victim cache comparison                      | 42 |

|    |      | 2.8.3. SBC behavior                                 | 43 |

|    |      | 2.8.4. Destination Set Selector efficiency          | 44 |

|    | 2.9. | Summary                                             | 45 |

| 3. | Bim  | odal Set Balancing Cache                            | 47 |

|    | 3.1. | Introduction                                        | 47 |

|    | 3.2.                                                                                           | Background and Motivation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 48                                                                                                                     |

|----|------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

|    | 3.3.                                                                                           | Bimodal Set Balancing Cache                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 51                                                                                                                     |

|    | 3.4.                                                                                           | Simulation environment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 54                                                                                                                     |

|    | 3.5.                                                                                           | Experimental evaluation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 54                                                                                                                     |

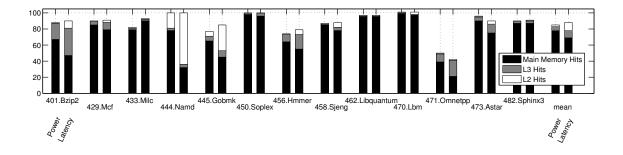

|    |                                                                                                | 3.5.1. Average memory latency and power consumption                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 60                                                                                                                     |

|    | 3.6.                                                                                           | Cost                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 60                                                                                                                     |

|    | 3.7.                                                                                           | Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 62                                                                                                                     |

|    |                                                                                                | 3.7.1. Impact of varying cache parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 62                                                                                                                     |

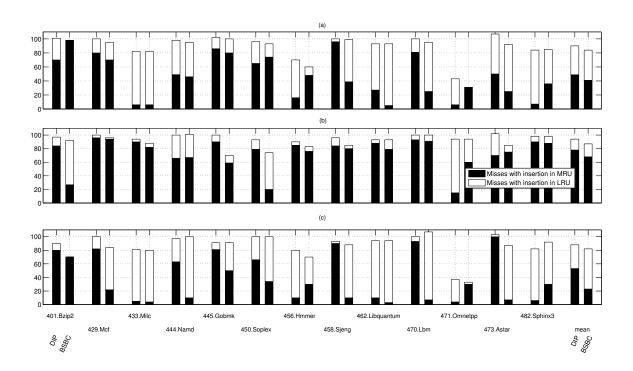

|    |                                                                                                | 3.7.2. BSBC behavior                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 63                                                                                                                     |

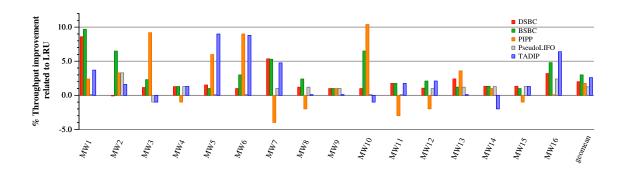

|    |                                                                                                | 3.7.3. Multicore experiments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 65                                                                                                                     |

|    | 3.8.                                                                                           | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 69                                                                                                                     |

|    |                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                        |

| 4. | Virt                                                                                           | tually Split Cache                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 71                                                                                                                     |

| 4. |                                                                                                | tually Split Cache                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | <b>71</b><br>71                                                                                                        |

| 4. | 4.1.                                                                                           | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 71                                                                                                                     |

| 4. | <ul><li>4.1.</li><li>4.2.</li></ul>                                                            | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 71<br>72                                                                                                               |

| 4. | <ul><li>4.1.</li><li>4.2.</li></ul>                                                            | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 71<br>72<br>75                                                                                                         |

| 4. | <ul><li>4.1.</li><li>4.2.</li></ul>                                                            | Introduction       Introduction         Background and Motivation       Introduction         Virtually Split Cache       Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 71<br>72<br>75<br>77                                                                                                   |

| 4. | <ul><li>4.1.</li><li>4.2.</li><li>4.3.</li></ul>                                               | Introduction       Introduction         Background and Motivation       Introduction         Virtually Split Cache       Introduction         4.3.1.       Shadow Tag VSC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | <ul> <li>71</li> <li>72</li> <li>75</li> <li>77</li> <li>78</li> </ul>                                                 |

| 4. | <ul><li>4.1.</li><li>4.2.</li><li>4.3.</li><li>4.4.</li></ul>                                  | Introduction       Introduction         Background and Motivation       Introduction         Virtually Split Cache       Introduction         4.3.1.       Shadow Tag VSC         4.3.2.       Global Selector VSC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | <ul> <li>71</li> <li>72</li> <li>75</li> <li>77</li> <li>78</li> <li>79</li> </ul>                                     |

| 4. | <ul><li>4.1.</li><li>4.2.</li><li>4.3.</li><li>4.4.</li></ul>                                  | Introduction       Introduction         Background and Motivation       Introduction         Virtually Split Cache       Introduction         4.3.1.       Shadow Tag VSC         4.3.2.       Global Selector VSC         Simulation environment       Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | <ul> <li>71</li> <li>72</li> <li>75</li> <li>77</li> <li>78</li> <li>79</li> <li>80</li> </ul>                         |

| 4. | <ul> <li>4.1.</li> <li>4.2.</li> <li>4.3.</li> <li>4.4.</li> <li>4.5.</li> </ul>               | Introduction       Introduction <td< td=""><td><ul> <li>71</li> <li>72</li> <li>75</li> <li>77</li> <li>78</li> <li>79</li> <li>80</li> <li>82</li> </ul></td></td<> | <ul> <li>71</li> <li>72</li> <li>75</li> <li>77</li> <li>78</li> <li>79</li> <li>80</li> <li>82</li> </ul>             |

| 4. | <ul> <li>4.1.</li> <li>4.2.</li> <li>4.3.</li> <li>4.4.</li> <li>4.5.</li> <li>4.6.</li> </ul> | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | <ul> <li>71</li> <li>72</li> <li>75</li> <li>77</li> <li>78</li> <li>79</li> <li>80</li> <li>82</li> <li>83</li> </ul> |

|    |                | 4.7.2. Multicore experiments                                            | 85  |

|----|----------------|-------------------------------------------------------------------------|-----|

|    | 4.8.           | Summary                                                                 | 87  |

| 5. | $\mathbf{Thr}$ | ead-Aware Bimodal Set Balancing Cache                                   | 89  |

|    | 5.1.           | Introduction                                                            | 89  |

|    | 5.2.           | Background and Motivation                                               | 90  |

|    | 5.3.           | Thread-Aware Bimodal Set Balancing Cache                                | 92  |

|    |                | 5.3.1. Unbalances among sets: Conflict Misses                           | 92  |

|    |                | 5.3.2. Lack of space in the cache: Capacity Misses                      | 93  |

|    |                | 5.3.3. BIP-C                                                            | 95  |

|    |                | 5.3.4. Computing Set Saturation Levels                                  | 96  |

|    |                | 5.3.5. Interaction between the Insertion and the Placement Policy $\ .$ | 97  |

|    |                | 5.3.6. Contribution of each policy to TABSBC performance                | 100 |

|    | 5.4.           | Simulation environment                                                  | 102 |

|    |                | 5.4.1. Metrics                                                          | 102 |

|    | 5.5.           | Experimental evaluation                                                 | 103 |

|    |                | 5.5.1. Average memory latency and power consumption                     | 107 |

|    | 5.6.           | Cost                                                                    | 107 |

|    | 5.7.           | Analysis                                                                | 109 |

|    |                | 5.7.1. Scalability analysis                                             | 109 |

|    |                | 5.7.2. Interaction with Prefetching                                     | 112 |

|    | 5.8.           | Summary                                                                 | 112 |

| 6. | Ada            | aptive Set-Granular Cooperative Caching                                 | 115 |

|    | 6.1.           | Introduction                                                            | 115 |

|    | 6.2.  | Backgr  | cound and Motivation                                         | . 116 |

|----|-------|---------|--------------------------------------------------------------|-------|

|    | 6.3.  | Adapti  | ive Set-Granular Cooperative Caching                         | . 120 |

|    |       | 6.3.1.  | Spilling-Aware BIP                                           | . 122 |

|    |       | 6.3.2.  | Design breakdown                                             | . 123 |

|    | 6.4.  | Adapti  | ive Variable-Granularity Cooperative Caching                 | . 125 |

|    |       | 6.4.1.  | Hardware description                                         | . 127 |

|    | 6.5.  | Simula  | tion environment                                             | . 128 |

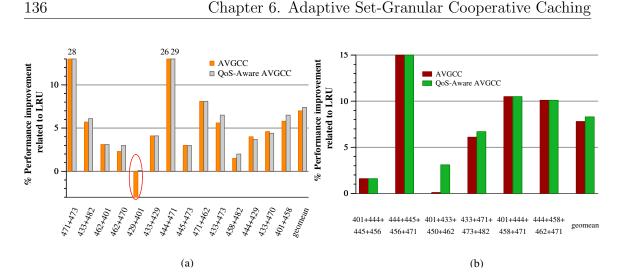

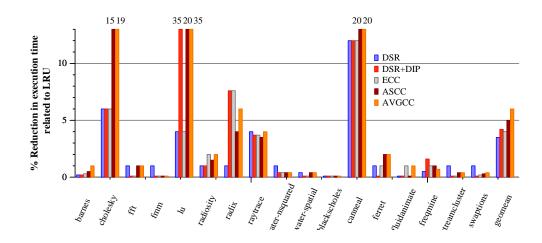

|    | 6.6.  | Experi  | mental evaluation                                            | . 129 |

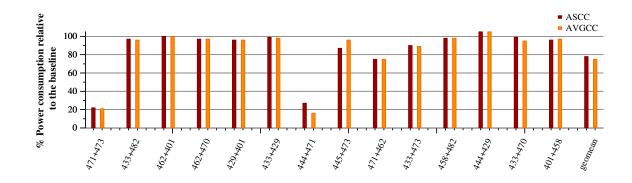

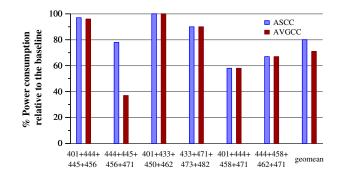

|    |       | 6.6.1.  | Average memory latency and power consumption $\ldots \ldots$ | . 134 |

|    | 6.7.  | QoS-A   | ware AVGCC                                                   | . 134 |

|    | 6.8.  | Cost .  |                                                              | . 137 |

|    |       | 6.8.1.  | Limiting the maximum number of counters                      | . 139 |

|    | 6.9.  | Analys  | $\sin$                                                       | . 139 |

|    |       | 6.9.1.  | Impact of varying cache parameters                           | . 139 |

|    |       | 6.9.2.  | Multithreaded experiments                                    | . 140 |

|    |       | 6.9.3.  | Interaction with Prefetching                                 | . 141 |

|    |       | 6.9.4.  | AVGCC behavior                                               | . 142 |

|    | 6.10. | Summa   | ary                                                          | . 142 |

| 7. | Con   | clusior | ns and Future Work                                           | 145   |

|    | 7.1.  | Conclu  | sions                                                        | . 145 |

|    |       |         | Work                                                         |       |

|    |       |         |                                                              | -     |

| А. | App   | endix   |                                                              | 153   |

|    | A.1.  | SBC a   | dditional experiments                                        | . 153 |

| References 15 |          |                                            |  | 159 |       |    |       |

|---------------|----------|--------------------------------------------|--|-----|-------|----|-------|

|               | A.2.1.   | TABSBC using the RRIP replacement policy . |  |     | <br>• |    | . 155 |

| A.2.          | TABSB    | C additional experiments                   |  |     | <br>• |    | . 155 |

|               | A.1.2. ] | OSBC with Extra Tags                       |  |     | <br>• |    | . 154 |

|               | A.1.1.   | Master-Slave SBC                           |  | •   | <br>• | •• | . 153 |

## List of Tables

| 2.1. | Baseline configuration                                                        | 32 |

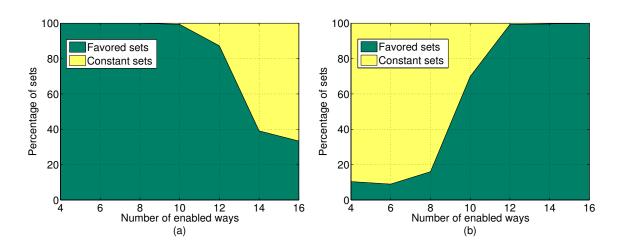

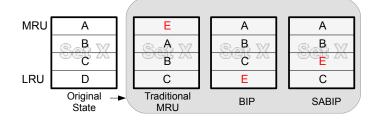

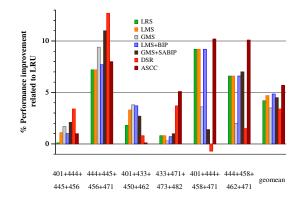

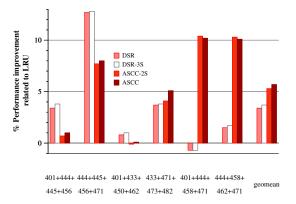

|------|-------------------------------------------------------------------------------|----|